Benefits of our courses

Money-back

guarantee

guarantee

If, within 30 days of placing your order, you discover that our courses do not meet your expectations, you will receive a full refund.

Experienced

instructors

instructors

Our instructors are highly experienced professionals and recognized authorities in the technical world.

Course

certificate

certificate

You will receive a course certificate upon completing coursework and finishing the course.

Practical

information

information

Our instructors share their knowledge and experience with you to make your learning process easier.

What you will learn in this course

1

Digital Logic

Introduction to digital logic, logic gates, and combinational logic. Introduction to the Makerchip online development environment. Labs include a calculator circuit.

2

Sequential Logic

Introduction to sequential logic. Labs include a counter and modifying the calculator to sequence calculations.

3

Pipelined Logic

Pipelining logic for high performance. Labs include pipelining the calculator circuit.

4

Modeling Validity of Signals and State

Modeling the validity of computations and its benefits for error checking, debugging, and reducing power with fine-grained clock gating. Modeling state that holds its value by default. Labs include adding validity (and therefore clock gating) as well as adding a single-value memory to the calculator circuit.

5

Basic CPU Microarchitecture

A typical microarchitecture of a single-cycle RISC-V CPU core. Overview of the CPU lab environment.

6

Instruction Fetching and Decoding

Concepts and lab exercises for developing logic to maintain the program counter (PC), fetch instructions, and decode instructions.

7

Register File, ALU, and Branching

Concepts and lab exercises for instantiating the register file for reading instruction operands and writing instruction results, performing computations for arithmetic instructions in the arithmetic logic unit (ALU), and executing branch instructions that modify the program counter.

8

Simple Pipelining of the CPU

Control flow hazards and data flow hazards in pipelined CPUs. Labs for pipelining the CPU core in a three-cycle pipeline with simple low-performance assumptions.

9

Improving Performance

Lab exercises that address hazards, including register forwarding/bypass logic. Completing instruction decode and ALU logic for a baseline (RV32I) RISC-V CPU core.

10

Data Memory, Loads, and Stores, and Jumps

Introduction to data memory operations. Labs to instantiate a data memory, load data from memory to registers, store data from registers to memory, and test memory instructions. Lab to add control logic for jump instructions. Course wrap-up.

Pricing Plans

Choose from three different pricing plans that meet your needs and expectations. Begin your learning journey today.

Online

$99

- Ideal for individuals

- Online video access for 12 weeks for 1 person

- Every online access can be extended for free for 1 month

- All lessons available immediately

- PDF Certificate (after completing activities) for 1 person

- 100% money-back guarantee (up to 30 days from order)

- Unlimited video access (once downloaded)

- Video download available

RECOMMENDED

Online and Download

$199

- Ideal for Individuals and Companies with smaller teams

- Online video access for 12 weeks for up to 3 people

- Every online access can be extended for free for 2 months

- All lessons available immediately

- PDF Certificate (after completing activities) for up to 3 people

- 100% money-back guarantee (up to 30 days from order)

- Unlimited video access (once downloaded)

- Video download available after 30 days

Quick Download

$249

- Ideal for Professionals and Companies with more than 3 engineers

- Online video access for 12 weeks for up to 5 people

- Every online access can be extended for free for 3 months

- All lessons available immediately

- PDF Certificate (after completing activities) for up to 5 people

- 100% money-back guarantee (up to 30 days from order)

- Unlimited video access (once downloaded)

- Video download available immediately

Frequently asked questions about the course

Related Courses

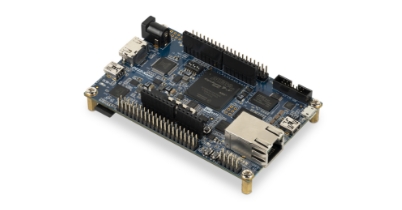

FROM$49

Learn the Essentials of VHDL and FPGA Development

You will learn how to start with VHDL and FPGA Programming. All the code and examples are explained in tutorin...